「TSMC N2的製程進展: 先進製程和先進封裝的融合」

TSMC即將在2025年的下半年量產2nm的製程,相對於3nm製程,2nm製程有架構性上的大更新。除此之外,TSMC也對2nm製程有一些製程上的優化。

其實從一些主要架構上的改變,我們可以看出目前先進製程上面的趨勢。

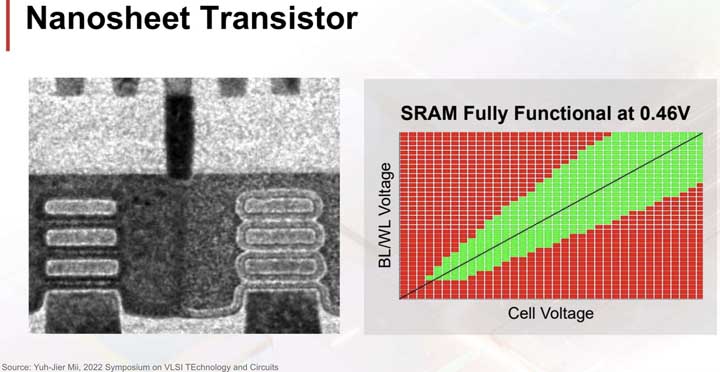

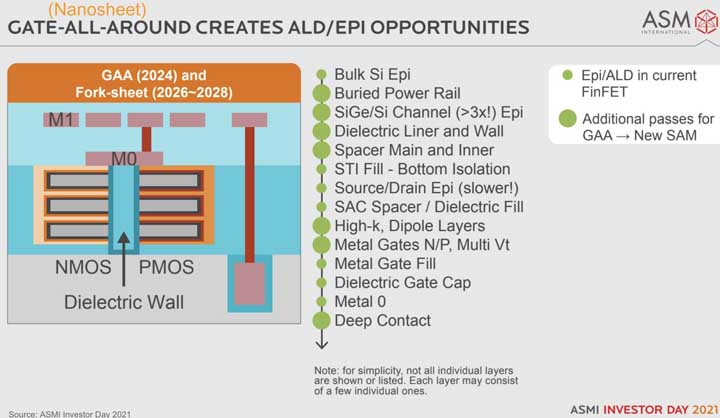

相對於FinFET, TSMC N2採用GAA (Nanosheet) 架構,相信大家也很好奇有什麼新的製程被採用?所以,這邊我們也挑幾個相對於FinFET製程來說比較特別的點,來跟大家討論一下~

(1). Gate-All-Around (GAA):決勝的關鍵在誰能做好製程控制

首先,最大的改變當然就是GAA (Nanosheet)的架構使用,這也是先進製程要往下延伸所需要做的最大架構改變。

在線寬的持續微縮下,FinFET架構已經無法再維持對漏電流的控制,因此,轉換到GAA架構是必要的一步。

這象徵了先進製程往更複雜的3D結構演化,不過,隨之而來的挑戰就會是更複雜的3D結構檢測以及製程控制。

另外,超過2000道製程步驟的複雜度,也會是對半導體製造良率的挑戰,因此,對於製程控制的經驗和技術好壞,會是半導體廠能力的分野。

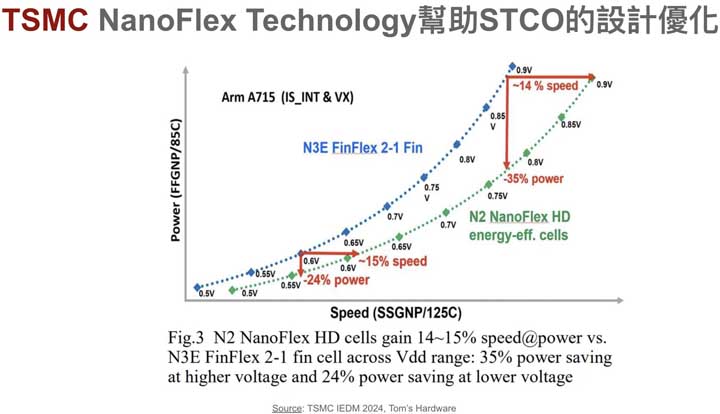

(2). NanoFlex Technology:提升DTCO / STCO的設計彈性

而在N2,TSMC也提供了所謂的NanoFlex選項,也就是客戶可以根據其設計需求,去調整GAA (Nanosheet) 的Cell尺寸,short cell可以有更小的尺寸與更好的power efficiency,而tall cell可以有更好的效能。

可以調整尺寸的好處是,客戶可以根據需求,去做所謂的Design Technology Co-Optimization (DTCO),根據他想要的性能&尺寸目標去做優化。

但是NanoFlex的重點不只是在GAA (Nanosheet)寬度的調整,而是在整體半導體System Technology Co-Optimization (STCO) 的設計角度下,NanoFlex能和TSMC的3DFabric先進封裝技術做共同優化,對AI, Mobile, HPC……等各種不同產品的要求去做STCO系統設計上的優化。

這邊可以看到,在晶片越來越往客製化的方向走的時候,製程上面可以做調整的部份也會越來越多。

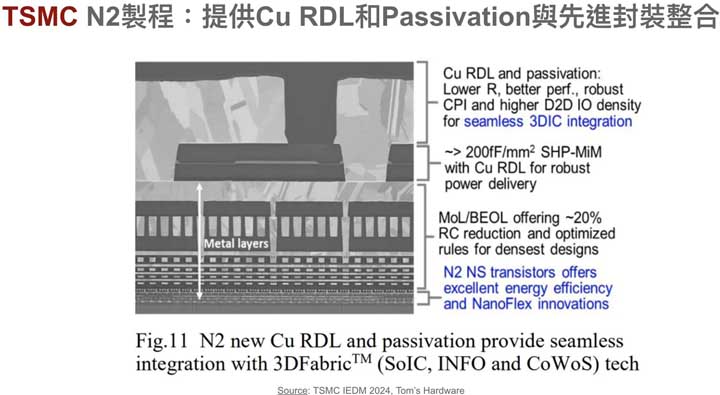

(3). 延伸先進製程介面,方便和先進封裝串接

所以其實在TSMC N2的設計上,TSMC有考慮到製程上要怎麼去和先進封裝做串接。TSMC在N2技術平台上,有提供Cu RDL和Passivation,幫助製程可以和先進封裝技術做更好的整合。

這邊我們可以觀察到,TSMC在製程上面已經不單單只是考慮先進製程了,因為他的GPU,CPU……等晶片製造客戶,已經大量在整合先進製程和Chiplet的設計,所以,我可以看到其在製造平台上面的演進。

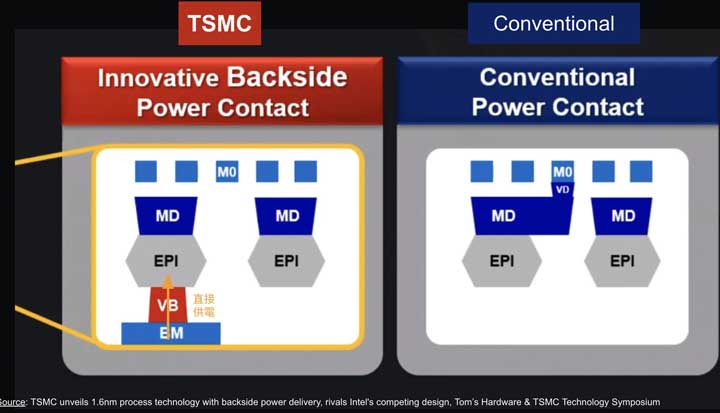

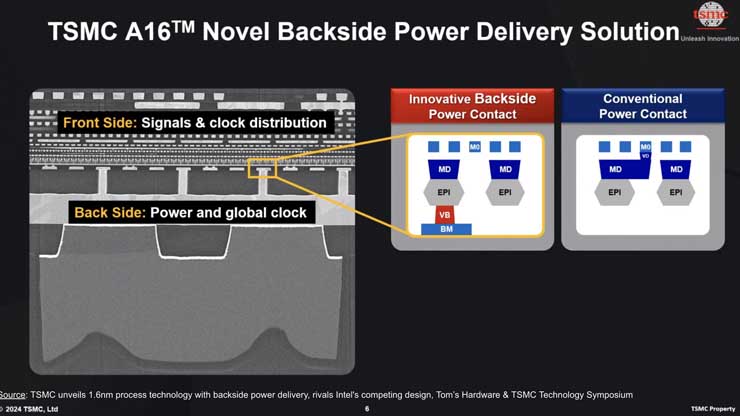

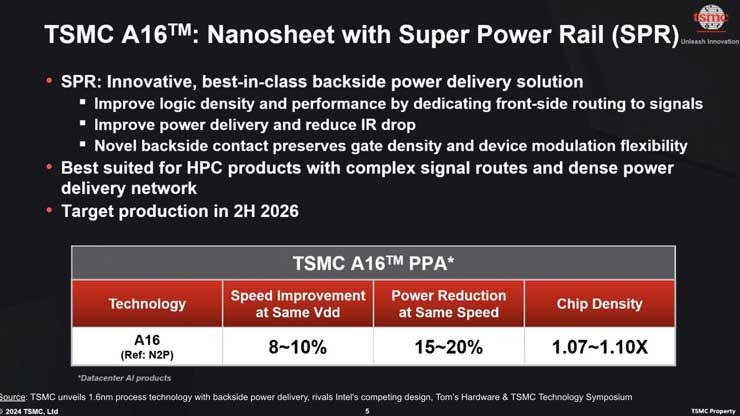

(4). 下一步 (A16製程):Backside Power Distribution

而再往下延伸,往下一個節點A16走,Backside Power Distribution 架構將會被引進。Backside Power Distribution的製程,其實也是大量串接先進製程和先進封裝。

因為,他要用uTSV的製程,和前端的GAA (Nanosheet)做串接。這在製程控制上面,也會是一個不小的挑戰。

TSMC和Intel在這上面,各自選擇的不同的路徑,而TSMC選擇的,會是較難但較效能更好的技術路徑,這在Wafer Bonding製程上,需要有較好的製程控制技術,才能做得好。

Conclusion: 先進製程和先進封裝製程的融合

所以我們從TSMC的製程發展裡面可以看得出來,目前先進製程的演進,已經開始大量的考慮和先進封裝端的整合,因為Chiplet的設計已經大量的進入最新的晶片設計中。

而也是因為這樣,在更多複雜的3D結構上,就會需要更好的製程控制技術,才能把接下來的節點做好。

前面我們大概解釋了TSMC N2製程的發展,

高雄廠二奈米上梁暨三廠動土典禮,被認為是要展現先進製程根留台灣的決心

嘉義太保的先進封裝廠也計畫擴充,加上買進群創舊廠改建的先進封裝廠,台積電未來在台投資金額預計超過三千億美元,相對於美國投資一千億美元尚未有明確時間表,供應鏈人士說,台積電規畫將最先進製程和先進封裝投資重心放在台灣,否則像荷商艾司摩爾、美商科林研發、日商東京威力科創、德商默克及蔡司不會無懼地緣政治風險仍來台擴大投資。

相關文章:

. https://udn.com/news/story/7240/8643907

積電高雄5座二奈米晶圓廠模型首曝光 總面積超過46座足球場