台積電3奈米需求超強,今年相關產能較去年大增三倍仍無法滿足客戶訂單,外傳已陸續祭出多項措施來擴充更多產能,並加速開出節奏並上修產能目標,相關訂單尚未包含英特爾CPU委外訂單。

台積電3奈米家族成員包含N3、N3E及N3P以及N3X、N3A等,既有N3技術持續升級之際,

N3E在2023年第4季量產瞄準AI加速器、高階智慧手機、資料中心等應用所需。

N3P預定2024下半年量產,估將成為2026年行動裝置、消費產品、基地台等主流應用;

至於N3X、N3A則是分別為高速運算、車用客戶等客製化產品打造。

N3、N3E、N3P、N3X、N3A、

Intel ULTRA 2 – Arrow Lake, Lunar Lake 處理器: 運算模塊是采用 N3B , GPU是 N5P , Soc、I/O模塊 TSMC N6

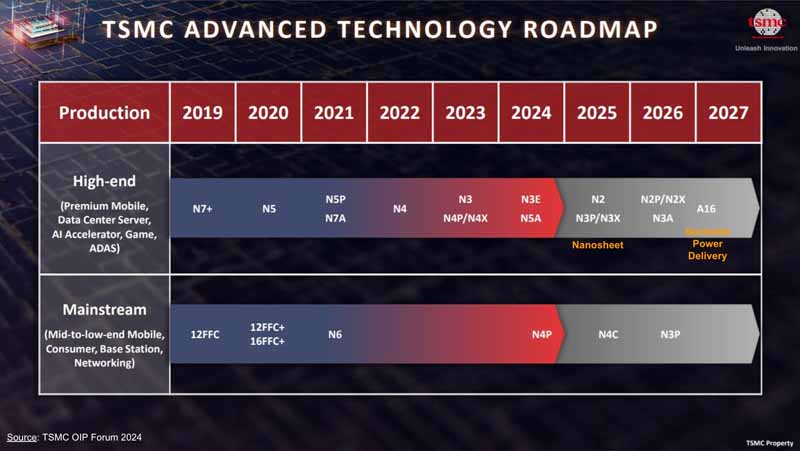

TSMC接下來的製程節點發展:N2 & A16」

目前N3是TSMC最新量產的先進製程,而接下來兩個新的節點,就會是TSMC的N2和A16。

這兩個新的節點對TSMC來說會是製程架構上面的改朝換代,因為N2會導入GAA製程,而A16會導入Backside Power Delivery。

大家可能會好奇這些新的製程架構相比於原本的製程有什麼不同?又有什麼新的挑戰?

我們就用這篇來快速介紹一下這兩個新的製程架構的發展。

★ TSMC N2 – 導入新的Nanosheet製程架構,製程複雜度再提升:

(1). 為何需要Nanosheet製程?:

相比於FinFET,Nanosheet的重點在於Gate與通道的接觸面積更多,能夠更好地控制漏電流,如果電晶體要再微縮的話,就必須要轉換到Nanosheet製程。

(2). 製程複雜度的提升:

而在製造上,其製程最大的特別之處,就是相比於FinFET製程,Nanosheet增加了很多磊晶和沈積的步驟。

所以,相比於之前的製程,N2製程步驟的數量也從早期的500或1000道製程步驟,到超過2000道的製程步驟。

這也顯示了Nanosheet製程的複雜度。

而這其實代表的是,在N2之後,整體的製程都將變得更複雜。而也因為Nanosheet的特殊結構,製程對於磊晶、ALD (Atomic Layer Deposition)、檢測&製程控制技術的需求都會變得更高。

(3). 未來發展:

不過,我們可以注意到的是,相較於前一代的製程,N2電晶體密度的提升並不多,大約在15%上下。

因此,我們可以推斷,N2相對於N3除了製程結構改變外,在線寬的尺寸上其實改變並不大。

因此,對於曝光機性能的需求改變可能也不會太大。

所以從目前的Roadmap看起來,第一代的Nanosheet製程主要做的會是製程架構的轉換,而接下來到1.4nm或1.0nm,會再將Nanosheet的結構再往下微縮。

而由於前面所說的,因為製程步驟數量大幅提升 (>2000道製程),因此對各家公司來說,製程控制和良率提升就會是未來的決勝點。

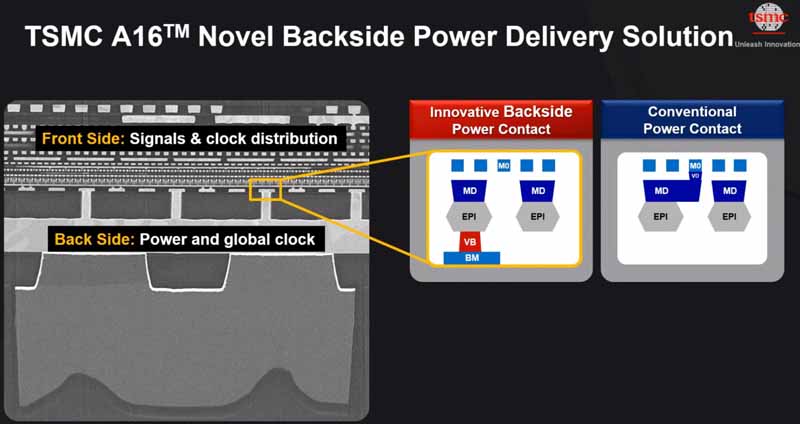

★ TSMC A16 – TSMC特殊的Backside Power Delivery製程,有助於對晶片能耗的未來需求:

(1). 為何需要Backside Power Delivery製程?:

Backside Power Delivery製程的好處,是因為他從晶圓背面供電,不用再經過原本放在晶圓正面做訊號傳輸的導線,因此大幅縮短供電路徑,因此能夠很好的降低能耗。

而據TSMC公布,接下來在A16節點,才會導入Backside Power Delivery架構,TSMC稱其為”Super Power Rail”。

(2). TSMC和Intel在Backside Power Delivery製程的方案比較:

TSMC有特別強調這個製程是innovative backside power contact的製程,想必一定有它特別的地方。

而我們將其跟Intel的PowerVia製程相比,發現TSMC採取了一個難度更高的解決方案。

如圖所示,TSMC的解決方案會直接從晶圓背後直接對電晶體供電,而Intel選擇的PowerVia方案會先用PowerVia先跟Trench Contact連接,再從側面對電晶體供電。

所以目前看來雖然Intel預計量產PowerVia的時程較早,但TSMC A16在2026下半年量產後,其方案將會是難度更高,效能更好的解決方案。

而對於能耗效率要求越來越高的HPC來說,Backside Power Delivery製程就是一個很好的解決方案。

★ 半導體先進製程接下來的發展

因此,我們會發現,先進製程的發展在2nm以後,為了解決微縮會有的漏電流問題,所有半導體廠都導入了新的架構,如Nanosheet。

另外,為了解決晶圓正面供電 (傳統的方式) 造成的過高能耗和發熱,大家也都選擇在類似的節點導入Backside Power Delivery晶背供電技術。

不過,由於量產最後看的還是製程最後的性能與良率,因此,最終的決勝點還是在哪家半導體廠能在製程複雜度、良率、性能和成本之前,達到最好的平衡。

而Nanosheet和Backside Power Delivery的製程,也會再被持續的優化幾代,然後再往下一個製程架構邁進。

台積電的2奈米(N2)製程在靜態隨機存取記憶體(SRAM)的密度上優於英特爾的1.8奈米(18A)製程。根據2025國際固態電路研討會(2025 ISSCC)先進計畫,英特爾的18A SRAM密度大幅低於台積電的N2,較接近台積電的3奈米(N3),不過,相較台積電的N2,英特爾的18A可能仍有其他重要優勢。

報導說,英特爾18A製程的特點是具有 0.021 µm^2 的高密度 SRAM 位單元尺寸(因此達成約 31.8 Mb/mm^2 的 SRAM 密度),這與台積電N3E與N5提供的一致。相較之下,台積電N2製程技術將 HD SRAM 位單元尺寸縮小至 0.0175 µm^2 左右,使 SRAM 密度達到 38 Mb/mm^2